3D-COSTAR tool

Delft, the Netherlands and Leuven, Belgium – October 8, 2013 – Delft University of Technology (TU Delft) and nanoelectronics research center imec, today presented 3D-COSTAR, a new test flow cost modeling tool for 2.5/3D stacked integrated circuits (ICs). 3D-COSTAR aims to optimize the test flow of 3D stacked ICs (SICs), taking into account the yields and costs of design, manufacturing, packaging, test, and logistics.

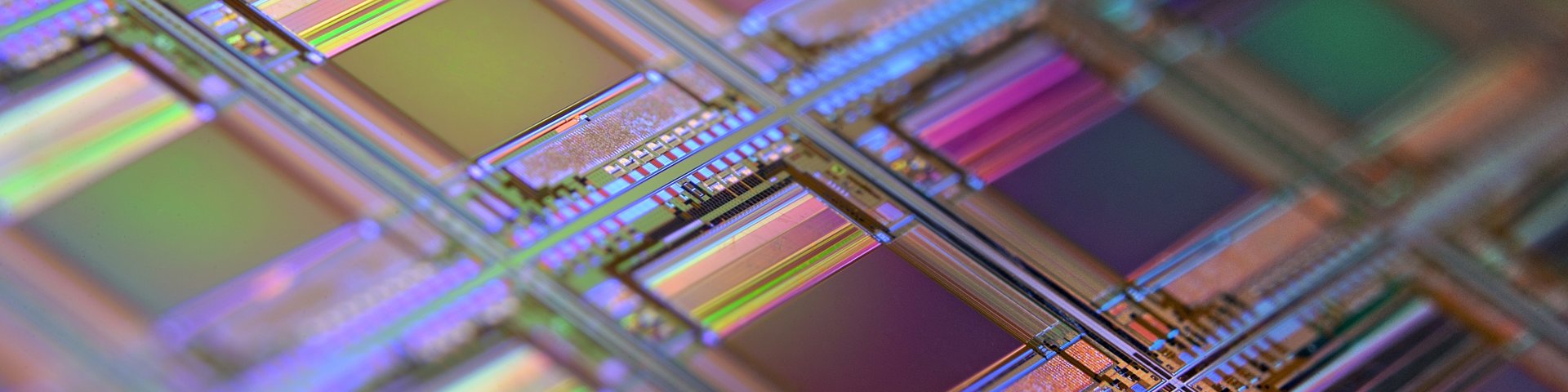

Due to its many high-precision steps, semiconductor manufacturing is defect-prone. Consequently, every IC needs to undergo electrical tests to weed out defective parts and guarantee outgoing product quality to the customer. For TSV-based 2.5D- and 3D-SICs that typically contain complex die designs in advanced technology nodes, testing is even more critical. In addition, there are many possible test moment in their manufacturing flow: pre-bond (before stacking), mid-bond (on a partial stack), post-bond (on a completed stack), and final testing (on a packaged device). Although testing is expensive, filtering out the bad components in an early stage is critical to save costs later on in the production process.

“There is not a ‘one-size-fits-all’ test flow that covers all stacked-die products. The test flow needs to be optimized based on yield and cost parameters of an individual product and that is a complex optimization problem,” stated Dr. Said Hamdioui, Associate Professor at TU Delft. “And different test flows, executed after manufacturing, may require different design-for-test features, which need to be incorporated in the various dies during their early design stages.”

3D-COSTAR uses input parameters that cover the entire 2.5D-/3D-SIC production flow: 1) design; 2) manufacturing; 3) test; 4) packaging; and 5) logistics. It is aware of the stack build-up (2.5D versus 3D, multiple towers; face-to-face or face-to-back) and stacking process (die-to-die, die-to-wafer, or wafer-to-wafer). The tool produces three key analysis parameters: 1) product quality, expressed as defect level (test escape rate) in DPPM (defective parts per million); 2) overall stack cost; and 3) breakdown per cost type.

“3D-COSTAR has proven to be a crucial tool to analyze the many complex trade-offs in 3D test flows, in terms of both cost and DPPM,” said Erik Jan Marinissen, Principal Scientist at imec. “Among others, we have used 3D-COSTAR to determine when pre-bond testing of the interposer in 2.5D-SICs pays off and what its maximum-allowed test cost can be. In some cases, the overall stack cost reduction amounts to 40%, showcasing that upstream testing can help avoid downstream costs. The tool also demonstrated under which circumstances mid-bond testing (on partially-completed stacks) can be avoided without compromising a high stack yield.”

“Together with imec, Cascade Microtech has recently demonstrated the feasibility of direct probing large-array fine-pitch micro-bumps to avoid the usage of dedicated pre-bond pads,” stated Ken Smith, Principal Engineer, Cascade Microtech, Inc. (of Beaverton, Oregon, USA). “Analysis with 3D-COSTAR clearly showed up to 50% overall cost benefit of doing microbump probing using an advanced probe cell such as was demonstrated with Pyramid Probe® RBI technology on our CM300 probe station.

See also the following papers showing case studies and the added value of 3D-COSTAR:

- Mottaqiallah Taouil, Said Hamdioui, Kees Beenakker, Erik Jan Marinissen: Test Impact on the Overall Die-to-Wafer 3D Stacked IC Cost. J. Electronic Testing 28(1): 15-25 (2012)

- Mottaqiallah Taouil, Said Hamdioui, Erik Jan Marinissen, Sudipta Bhawmik: Impact of mid-bond testing in 3D stacked ICs. DFT 2013: 178-183.

- Mottaqiallah Taouil, Said Hamdioui, Erik Jan Marinissen, Sudipta Bhawmik: Using 3D-COSTAR for 2.5D test cost optimization. 3DIC 2013: 1-8.

- Mottaqiallah Taouil, Said Hamdioui, Erik Jan Marinissen: Quality versus cost analysis for 3D Stacked ICs. VTS 2014: 1-6

- Erik Jan Marinissen, Bart De Wachter, Ken Smith, Jorg Kiesewetter, Mottaqiallah Taouil, Said Hamdioui: Direct probing on large-array fine-pitch micro-bumps of a wide-I/O logic-memory interface. International Test Conference ITC, 2014: 1-10.

Manual

Please download the manual here.

Examples

Three example input files are made available.

Click here to open the 2.5D-SIC example.

Click here to open the 3D-SIC example.

Click here to open the 5.5D-SIC example.

For more information about this tool, please contact M. Taouil