Research

Heterogeneity, real-time performance adaptivity to computational load and surrounding environmental variability, fault tolerance, massive parallelism, high speed, ultra-low energy, all these are precepts that guide the innovations propelling next generation sustainable computing. Our research group is focused on Graphene nano-devices and Spin Wave based circuits, architectures, and novel computational paradigms, that seek to complement existing CPU, GPU, and FPGA technologies on one hand, and to extend and redefine the tenets of "traditional" Turing - von Neumann computing on the other hand. To this end we mainly concentrate on three main research avenues as follows.

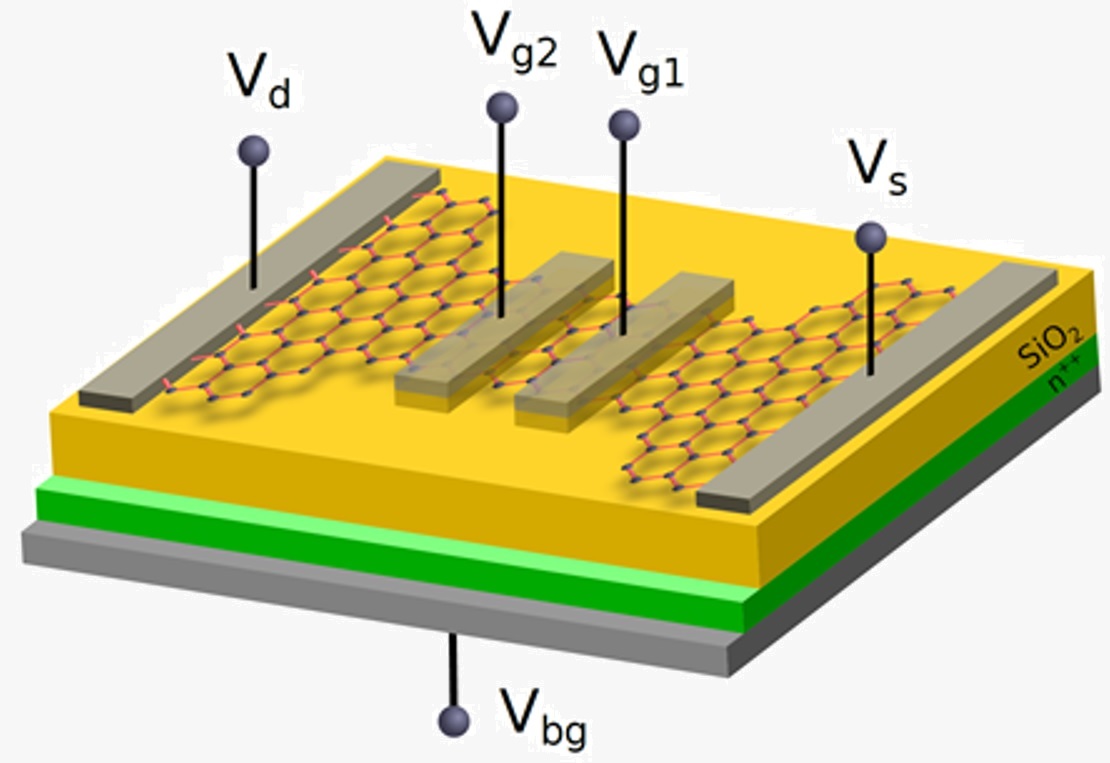

Graphene-based Logic and Circuits

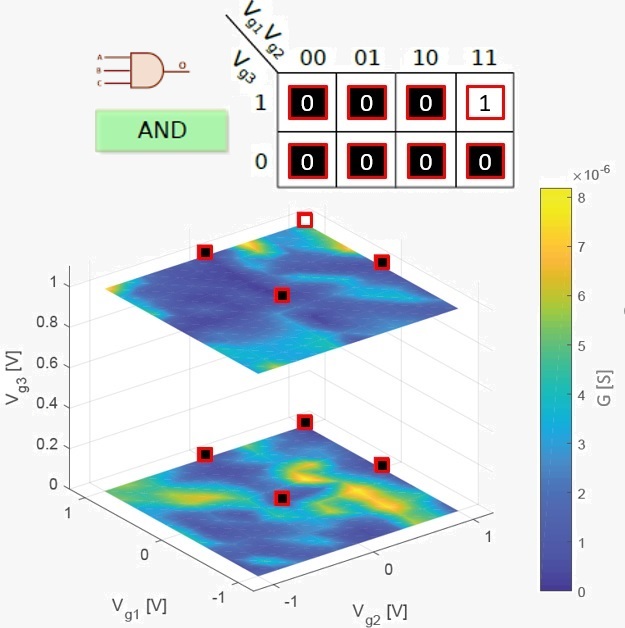

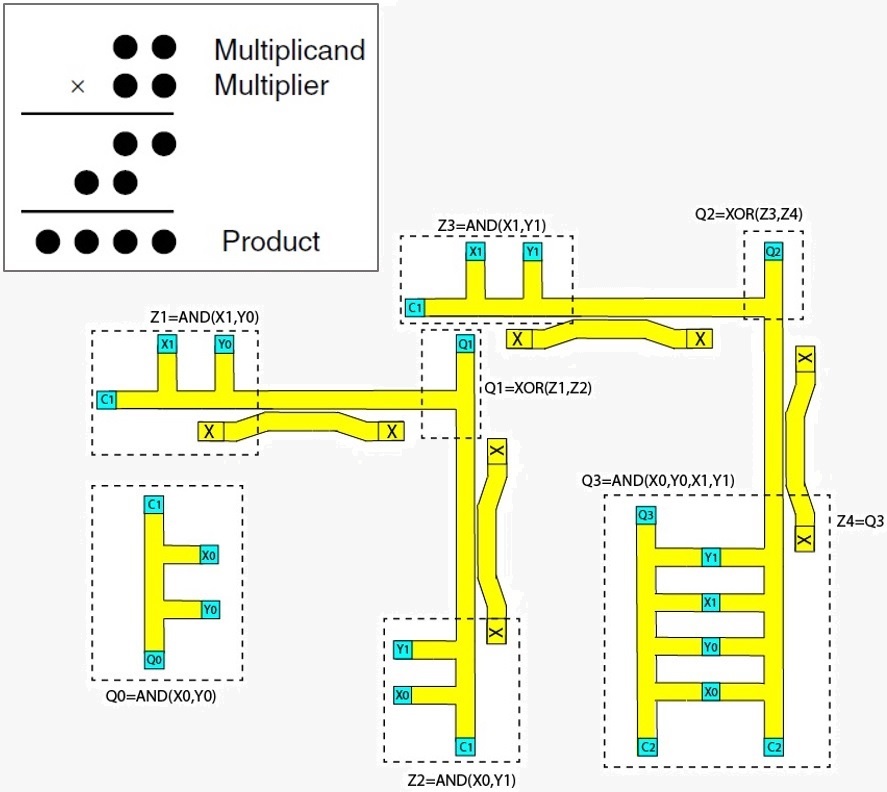

Generally speaking, the main impediments to graphene-based logic from the circuit design standpoint concern the ability to: (i) control graphene's conductivity and yield distinguishable ”On” and ”Off” states, while (a) not compromising any of the graphene intrinsic highly advantageous properties (e.g., high carrier mobility), and (b) providing an ION / IOFF ratio in the order of 106 to 107 (i.e., the typical ratio for low power < 20nm CMOS logic process), (ii) encode the desired logic transfer function into the graphene electrical characteristics (e.g., conduction maps), (iii) find proper external electric means (e.g., top gates, back gates) to control the graphene behavior and induce the desired logic functionality, and (iv) ensure logic gates cascading conditions (i.e., gate input-output electric levels matching). As graphene-based nanodevices comport fundamentally different than conventional CMOS devices they can be employed not as merely beyond-CMOS replacement switches, but as new information processing primitive elements able to fully exploit the graphene's inherent properties. For instance, as graphene's conductance is a nonlinear function on the voltages to which it is exposed, graphene coan potentially be utilized to emulate a much richer functionality than a simple transistor (e.g., one could do addition with a single piece of graphene, instead of using multiple transistors).

In these sub-theme we focus on the design (and implementation) of graphene-based Boolean logic and circuits, which can fully exploit graphene's excellent properties and that can offer a viable solution towards energy efficient computing. Recent research dealt with investigations into graphene 2- and 3-input Boolean gates based on a complementary design style [1], but also full adder and SRAM cells [2], which are essentially the fundamental components for the construction of any computation system.

Graphene-based Neuromorphic Computing

Recent years have gradually eroded many gaps between computers and human capabilities. Designing and constructing architectures that draw inspiration from human brain organizing philosophy and operation heralds a completely different, massively parallel, on a smaller footprint, much faster, and highly energy efficient manner of computation and communication, not only for neuromorphic systems, but perhaps for general-purpose computing systems as well.

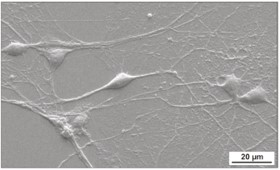

Our research is focused on pursuing innovations in emerging neuromorphic computational paradigms and their afferent graphene-based infrastructure (design and implementation from device-level to architecture-level to system-level). In this context, we seek to answer several questions among which:

- What are the fundamental computational units vis-a-vis the neural spatio-temporal scale (neurons, synapses, network of neurons, etc.)?

- What is the most appropriate encoding of information?

- Which are the neural dynamics that are relevant for computing?

- How should the fundamental computational units work together and give rise to architectures?

- How to approach a computational problem to architecture mapping?

Recent research dealt with investigations into low-energy neural basic building blocks (graphene-based spiking neurons [3] and plastic synapses [4] circuitry) and proof-of-concept spiking neural networks architectures that utilize the graphene-based neural components for several application scenarios [5].

Spin Wave Computing

The fascination of playing with the electron spin is quite old, yet today's computing is mostly based on electrical signals and charges where the spin is almost always used solely for information storage purposes. Spin waves interaction offers a new angle on calculation that departs from traditional charge-based electronics and creates the premises for 'democratic' majority computation, which is fundamental for error correcting codes and known to yield highly compact circuits for computation in general, but yet mostly overlooked thus far because of the high power consumption incurred by the CMOS technology majority gate implementations. The highly parallel nature of wave propagation and the ability to process data by appropriately designed spin waves interference patterns, offer a new way to compute where the energy and delay are largely decoupled (once waves are generated, moving them around regardless of their speed, require virtually no energy), and can potentially be a "Holy Grail" of the current technologies energy landscape crisis.

Our research is focused on spin wave computing paradigms and circuits that can complement and eventually replace CMOS. In this context, we focus on majority devices design and on overcoming the challenges associated with connecting these majority devices in order to build logic circuits. We are targeting hybrid CMOS-spin wave architectures in which the data processing is mostly (ideally entirely) performed in spin wave computation islands, while the interaction with the CMOS environment is limited to input data acquisition and output data reporting. Recent research dealt with investigations into, e.g., fanout achievement [6], gate cascading [7], and multi frequency enabled data processing parallelism [8].