Research

Our research is focused on 3 domains with the following challenges:

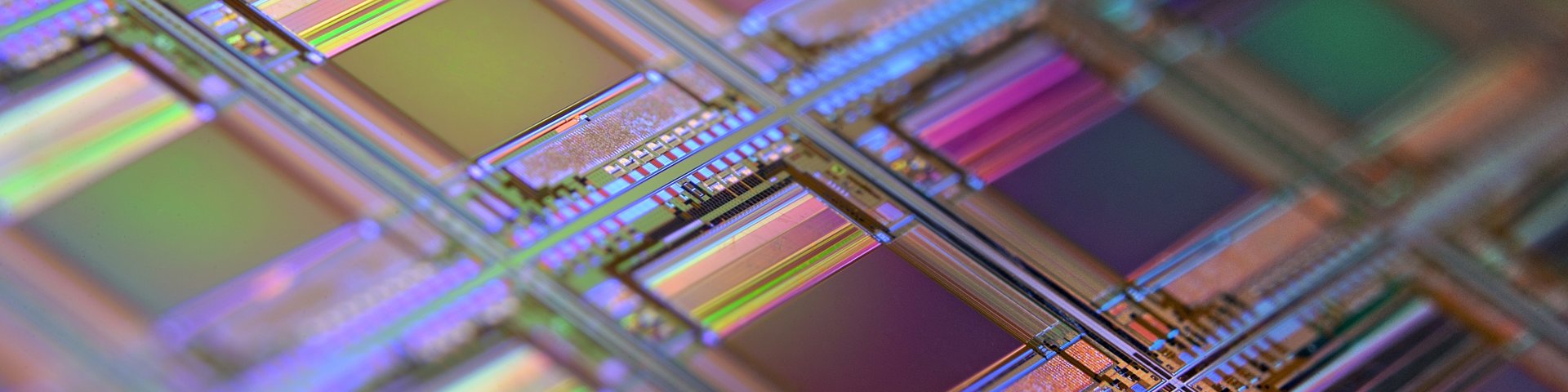

- Liquid Architectures: Due to the increased System-on-Chip (SoC) complexity where adaptivity, reconfigurability and composability are viewed as key system features, this line of research investigates how to make e.g. the processor architecture runtime adaptable to the application requirements and the available hardware resources. Topics are: workload characterization, hardware/software co-design, reconfigurable VLIW processor architectures (rVEX).

- Dependable Nano Computing: Driven by three major challenges: 1) technology scaling (causing extreme variability, reduced reliability, …), 2) globalization of IC supply chain (demanding re-assess of trust in hardware, IP protection, …) and 3) Internet of things (demanding secure End-to-End solutions, user privacy & data protection, …) , this research pillar focuses on three topics: 1) Reliability (including modelling, monitoring, mitigation, ….), 2) Testability (including Fault Modeling and Design-for-Testability for 3D stacked ICs and emerging memories), and 3) Hardware security (including PUF technology, secure design, etc).

- In-Memory Computing: One of the most critical challenges for today’s and future data-intensive and big-data problems is data storage and analysis. The primary goal is to increase the understanding of processes by extracting highly useful values hidden in the huge volumes of data. The increase of the data size has already surpassed the capabilities of today’s computation architectures, which suffer from the limited bandwidth, energy inefficiency and limited scalability. In-Memory-Computing research targets the development, the design and the demonstration of a new architecture paradigm for big data problems; it is based on the integration of the storage and computation in the same physical location (using a crossbar topology) and the use of non-volatile resistive-switching technology, based on memristors, instead of CMOS technology.